# RB-OLITS: A Worst-case Reorder Buffer Size Reduction Approach for 3D-NoC

**Zhenmin Li**, Yuqing Ma, Gaoming Du, Xiaolei Wang, Yukun Song, Duoli Zhang

School of Microelectronics, Hefei University of Technology, Hefei, China

## Background

- Preliminaries

- Worst-case Size Reduction of Reorder Buffer

- Experiments and Results

## Conclusion

# Background

- 3D-NoC is emerging as a promising successor to the traditional bus-interconnecting architecture in MPSoC designs

- The packet based 3D-NoC paradigm is highly scalable and fundamentally decouples communication from computation

- In-order packet delivery is crucial for a majority of applications, for instance, multimedia or cache coherence protocols

- Packets arriving at the destination may cause the out-of-order problem

- Calculation and reduction of worst-case reorder buffer size has become a pivotal research topic.

## Background

## Preliminaries

- Worst-case Size Reduction of Reorder Buffer

- Experiments and Results

## Conclusion

# **Preliminaries**

## Background

## Preliminaries

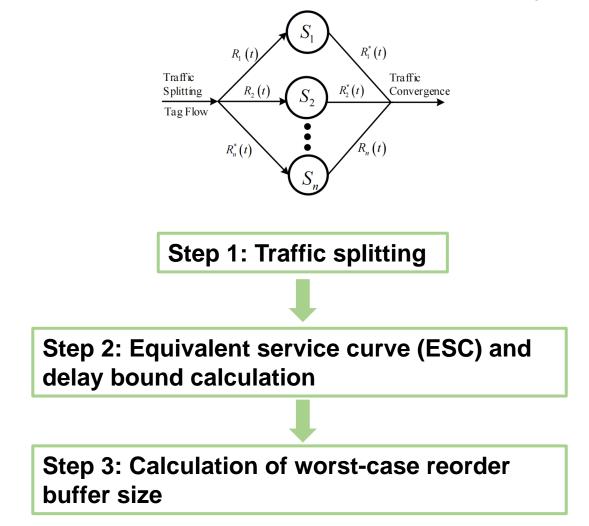

## Worst-case Size Reduction of Reorder Buffer

Experiments and Results

## Conclusion

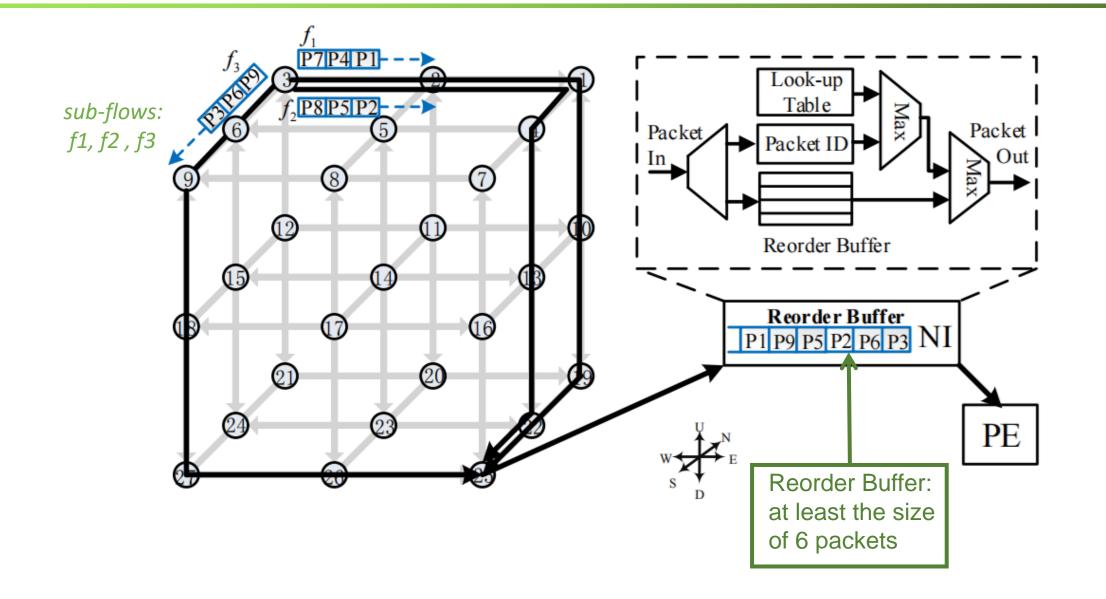

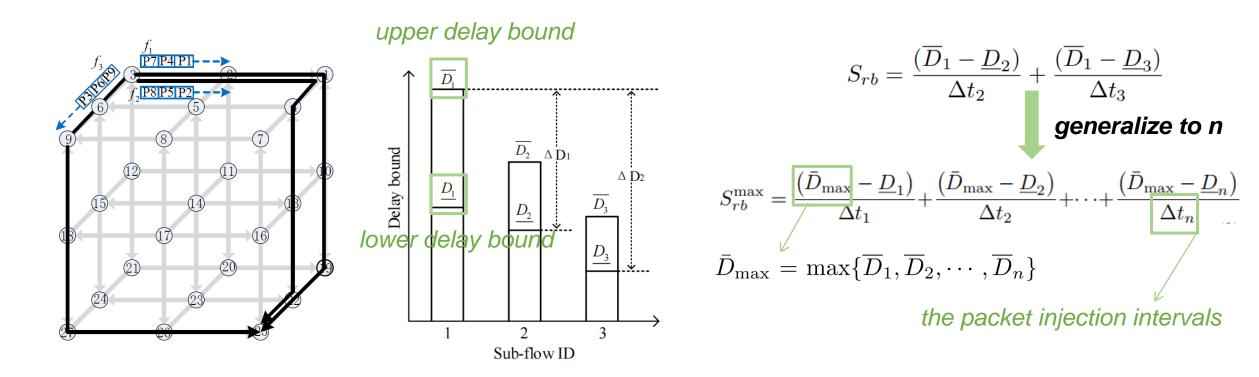

### **Motivating Example**

#### Worst-case Reorder Buffer Size Analysis Based on Network Calculus

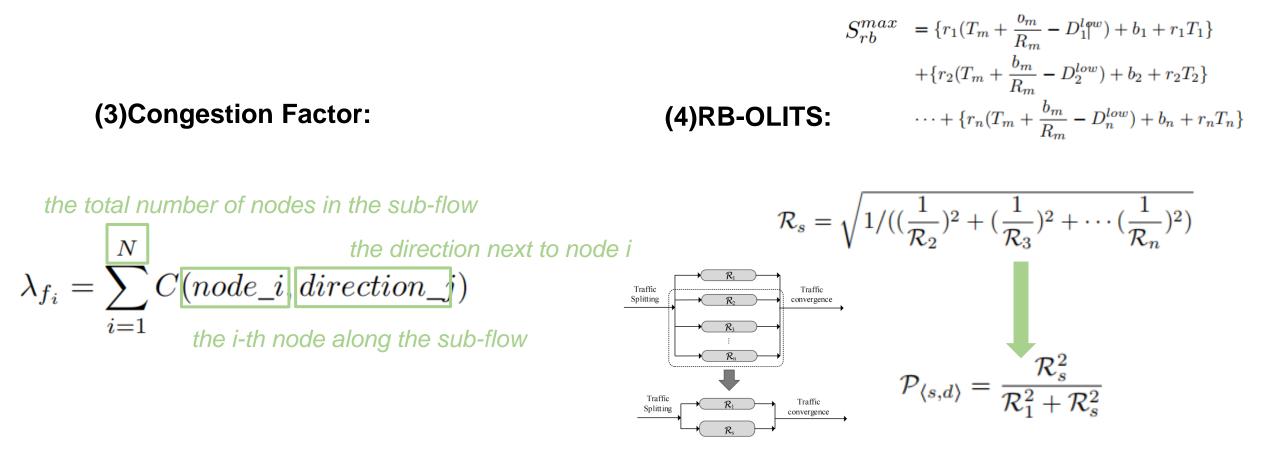

$$\begin{split} S_{rb}^{max} &= \{R_m^*\left(t\right) - R_1^*\left(s\right)\} + \{R_m^*\left(t\right) - R_2^*\left(s\right)\} \\ &\cdots + \{R_m^*\left(t\right) - R_n^*\left(s\right)\} \\ &= \alpha_1^*\left(\Delta t_1\right) + \alpha_2^*\left(\Delta t_2\right) \cdots + \alpha_n^*\left(\Delta t_n\right) \\ &= \{r_1\left(\Delta t_1\right) + b_1 + r_1T_1\} \\ &+ \{r_2\left(\Delta t_2\right) + b_2 + r_2T_2\} \\ &\cdots + \{r_n\left(\Delta t_n\right) + b_n + r_nT_n\} \\ &= \{r_1\left(h\left(\alpha_m, \beta_m\right) - D_1^{low}\right) + b_1 + r_1T_1\} \\ &+ \{r_2\left(h\left(\alpha_m, \beta_m\right) - D_2^{low}\right) + b_2 + r_2T_2\} \\ &\cdots + \{r_n\left(h\left(\alpha_m, \beta_m\right) - D_n^{low}\right) + b_n + r_nT_n\} \\ &= \{r_1(T_m + \frac{b_m}{R_m} - D_1^{low}) + b_1 + r_1T_1\} \\ &+ \{r_2(T_m + \frac{b_m}{R_m} - D_2^{low}) + b_2 + r_2T_2\} \\ &\cdots + \{r_n(T_m + \frac{b_m}{R_m} - D_n^{low}) + b_n + r_nT_n\} \end{split}$$

#### (1) Adjacency Matrix:

$A = (a_{ij})_{v \times 6}$   $a_{ij} = \begin{cases} p_{ij}, \text{ splitting propotion in } j \text{ direction at node } v_i \\ 0, \text{ else} \end{cases}$

#### (2)Contention Matrix:

flow rate and burstiness of sub-flow i

$$C_{s_i,d_i} = [(\varepsilon r_1 + \beta b_1)A_{s_1,d_1} + (\varepsilon r_2 + \beta b_2)A_{s_2,d_2} + \cdots + (\varepsilon r_j + \beta b_j)A_{s_j,d_j} + \cdots + (\varepsilon r_k + \beta b_k)A_{s_k,d_k}] \wedge A_{s_i,d_i}, j \neq i$$

$\epsilon$  and  $\beta$  are the impact factor of ri and b

## Background and Motivation

- Preliminaries

- Worst-case Size of Reorder Buffer

- Experiments and Results

- Conclusion

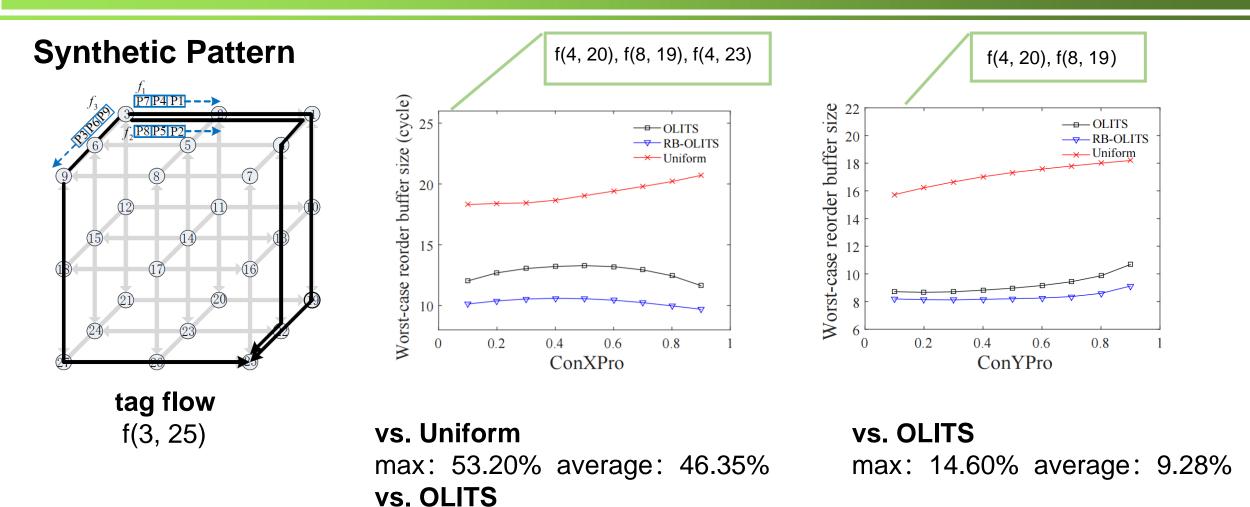

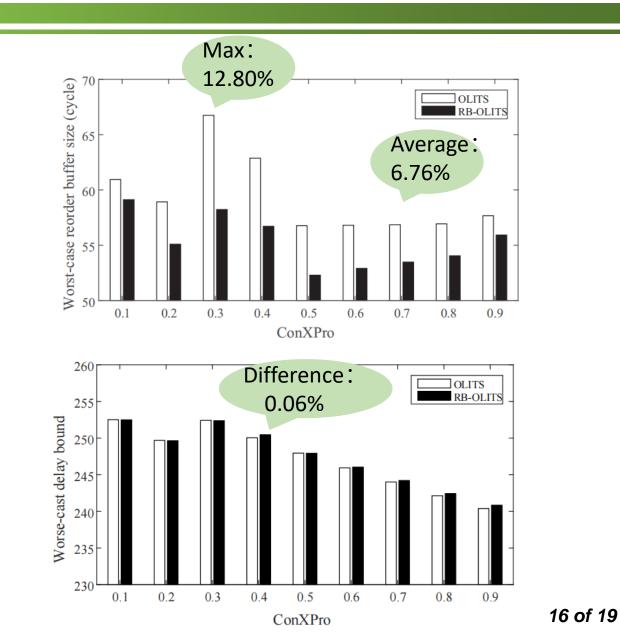

max: 20.88% average: 19.09%

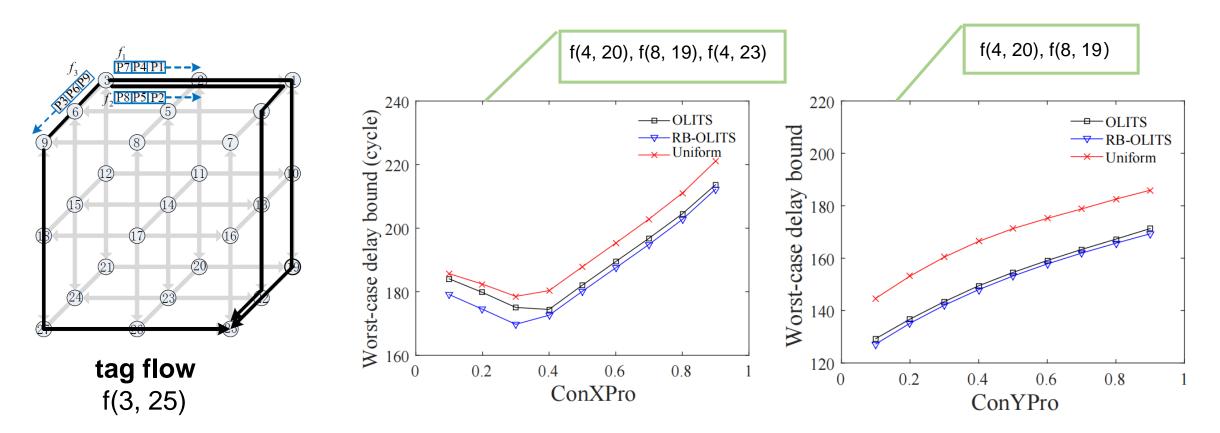

**Synthetic Pattern**

#### **Synthetic Pattern:**

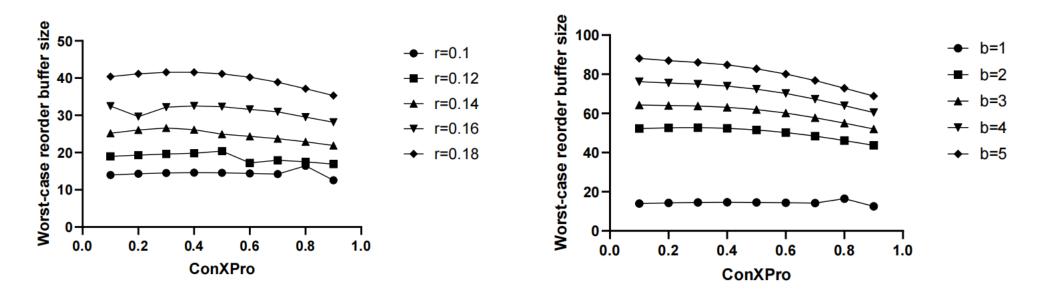

Impact of injection rate with varying bustiness

With the increasing injection rate or burstiness, the worst-case reorder buffer size increases accordingly

## Background

- Preliminaries

- Worst-case Size Reduction of Reorder Buffer

- Experiments and Results

## ■ Conclusion

# Conlusion

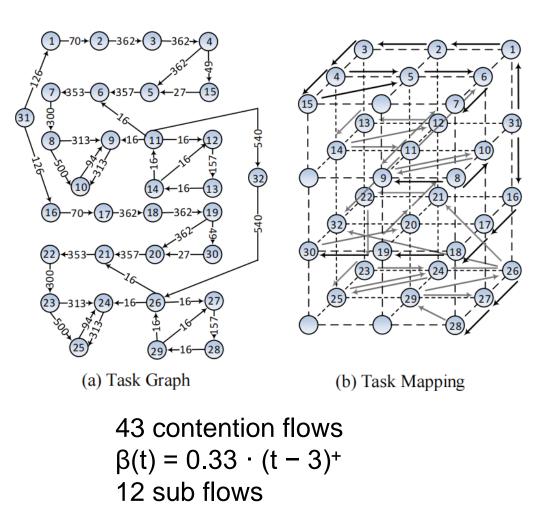

### An analytical model for calculating the worst-case reorder buffer size for multi-path minimal routing 3D-NoCs using network calculus

• support arbitrary number of sub-flows

■ A traffic splitting method, named RB-OLITS, for reducing worst case reorder buffer size.

• an improvement of 5.9%-20.9% in most cases